2024년 1학기 전기 전자 종합 설계 주제 안내

Author

comsys

Date

2023-12-27 12:00

Views

375

컴퓨터 시스템 및 고신뢰성 SOC 연구실에서

2024년도 1학기 진행될 종합 설계 연구 테마 관련하여 안내 드립니다.

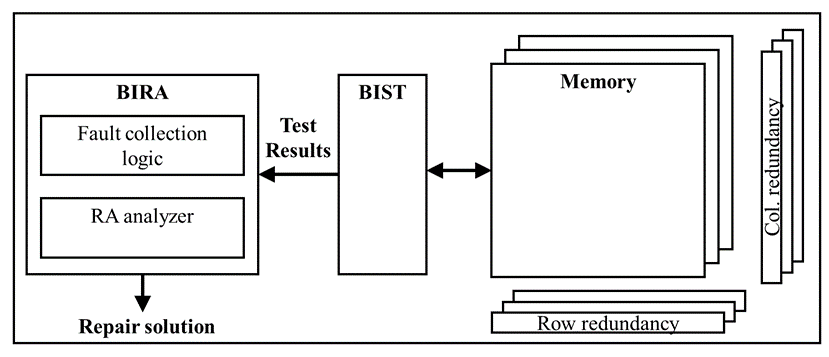

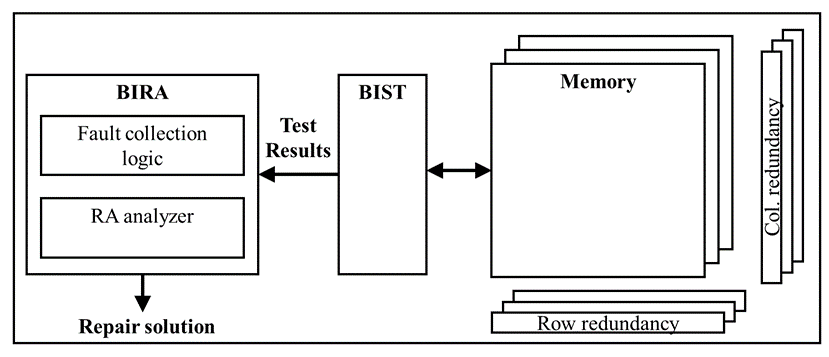

A. 고성능 BIRA (Built-In Redundancy Analysis) 회로 설계

자가 테스트 결과로부터 최적의 메모리 수리 솔루션을 도출하는 BIRA 회로 설계 및 동작 검증

그림 A. Memory BIRA 구조

-효율적으로 고장 정보를 저장하기 위한 fault collection logic 설계

-낮은 오버헤드와 높은 수리율을 달성하는 RA analyzer 회로 설계

-설계한 BIRA 회로에 대하여 테스트 툴을 활용한 성능 검증

※ RA (Redundancy Analysis)는 메모리에 존재하는 예비자원을 사용하여 고장이 있는 메모리 셀의 메모리 라인을 대체하여 수리하는 기법

※ BIST (Built-In Self Test) 모듈로부터 전달 받은 고장 정보를 분석하여 예비 자원을 효율적으로 배치하는 수리 솔루션 도출

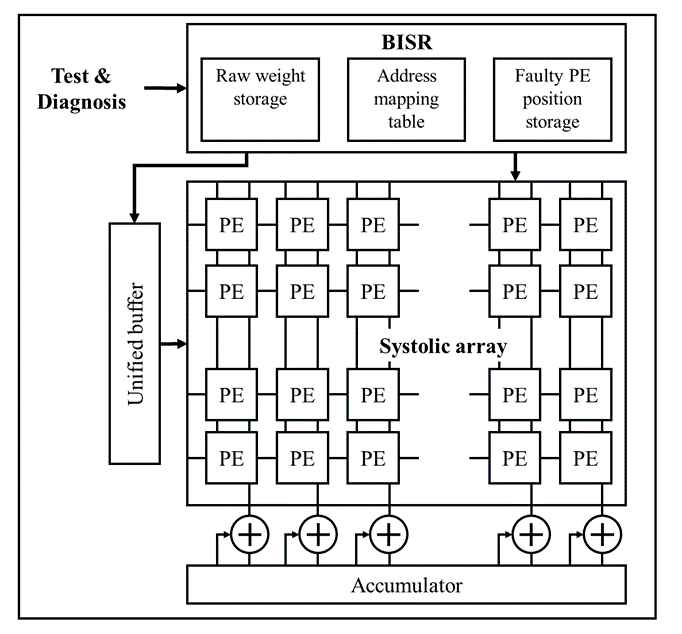

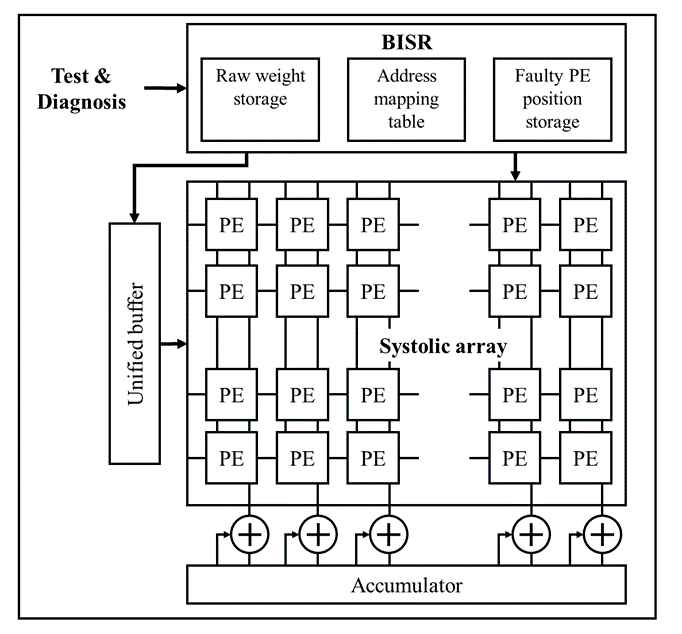

B. Reliable systolic array 설계

AI chip에 쓰이는 systolic array 설계 및 높은 reliability를 위한 BISR 회로 설계 및 검증

그림 B. Systolic array 및 BISR 구조

-PE (processing element) 및 systolic array 설계

-자가 테스트 결과를 사용하여 낮은 오버헤드와 높은 수리율을 달성하는 BISR 회로 설계

-설계한 BISR에 대하여 테스트 툴을 활용한 성능 검증

※ PE의 고장은 accumulation 되어 전체 연산에 큰 영향을 미침

※ Array size가 증가함에 따라 수리 알고리즘의 복잡도 증가 및 수리율의 감소 문제 존재

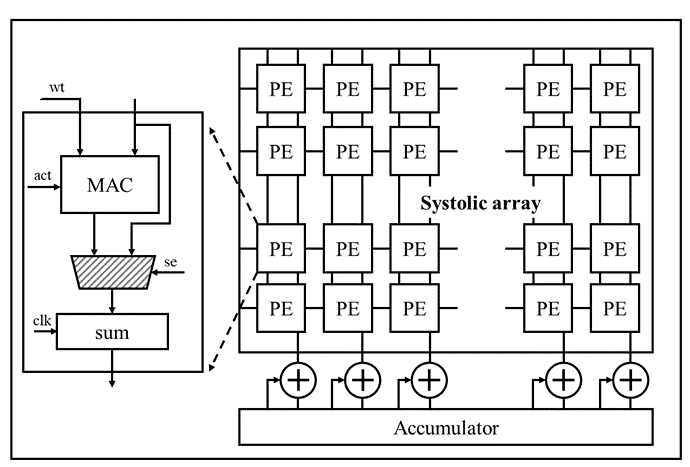

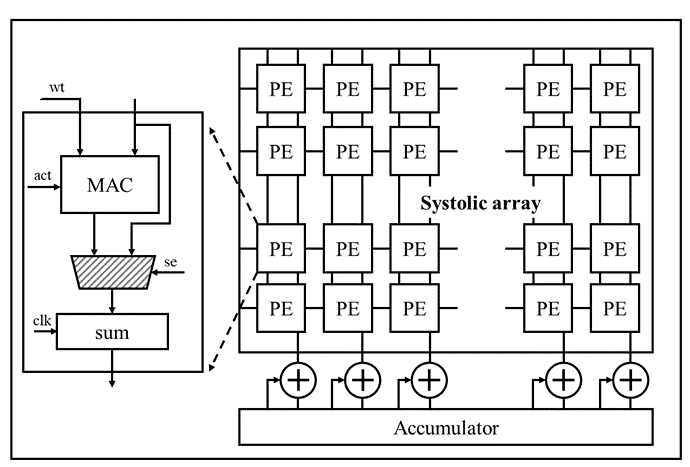

C. Testable systolic array 설계

AI chip에 쓰이는 systolic array 설계 및 높은 testability를 위한 DFT 회로 설계 및 검증

그림 C. DFT가 적용된 systolic array 구조

-PE (processing element) 및 systolic array 설계

-DFT 회로를 추가하여 높은 테스트 커버리지 및 낮은 오버헤드를 달성하는 회로 설계

-DFT를 추가한 전체 회로에 대하여 테스트 툴을 활용한 성능 검증

※ PE의 고장은 accumulation 되어 전체 연산에 큰 영향을 미침

※ Array size가 증가함에 따라 테스트의 복잡도가 증가하여 수율 확보가 어려움

2024년도 1학기 진행될 종합 설계 연구 테마 관련하여 안내 드립니다.

A. 고성능 BIRA (Built-In Redundancy Analysis) 회로 설계

자가 테스트 결과로부터 최적의 메모리 수리 솔루션을 도출하는 BIRA 회로 설계 및 동작 검증

그림 A. Memory BIRA 구조

-효율적으로 고장 정보를 저장하기 위한 fault collection logic 설계

-낮은 오버헤드와 높은 수리율을 달성하는 RA analyzer 회로 설계

-설계한 BIRA 회로에 대하여 테스트 툴을 활용한 성능 검증

※ RA (Redundancy Analysis)는 메모리에 존재하는 예비자원을 사용하여 고장이 있는 메모리 셀의 메모리 라인을 대체하여 수리하는 기법

※ BIST (Built-In Self Test) 모듈로부터 전달 받은 고장 정보를 분석하여 예비 자원을 효율적으로 배치하는 수리 솔루션 도출

B. Reliable systolic array 설계

AI chip에 쓰이는 systolic array 설계 및 높은 reliability를 위한 BISR 회로 설계 및 검증

그림 B. Systolic array 및 BISR 구조

-PE (processing element) 및 systolic array 설계

-자가 테스트 결과를 사용하여 낮은 오버헤드와 높은 수리율을 달성하는 BISR 회로 설계

-설계한 BISR에 대하여 테스트 툴을 활용한 성능 검증

※ PE의 고장은 accumulation 되어 전체 연산에 큰 영향을 미침

※ Array size가 증가함에 따라 수리 알고리즘의 복잡도 증가 및 수리율의 감소 문제 존재

C. Testable systolic array 설계

AI chip에 쓰이는 systolic array 설계 및 높은 testability를 위한 DFT 회로 설계 및 검증

그림 C. DFT가 적용된 systolic array 구조

-PE (processing element) 및 systolic array 설계

-DFT 회로를 추가하여 높은 테스트 커버리지 및 낮은 오버헤드를 달성하는 회로 설계

-DFT를 추가한 전체 회로에 대하여 테스트 툴을 활용한 성능 검증

※ PE의 고장은 accumulation 되어 전체 연산에 큰 영향을 미침

※ Array size가 증가함에 따라 테스트의 복잡도가 증가하여 수율 확보가 어려움