2025년 1학기 전기전자 종합설계 주제 안내

Author

comsys

Date

2024-11-13 15:57

Views

1153

컴퓨터시스템 및 고신뢰성 SOC 연구실에서

2025년도 1학기 진행될 종합설계 연구테마 관련하여 안내 드립니다.

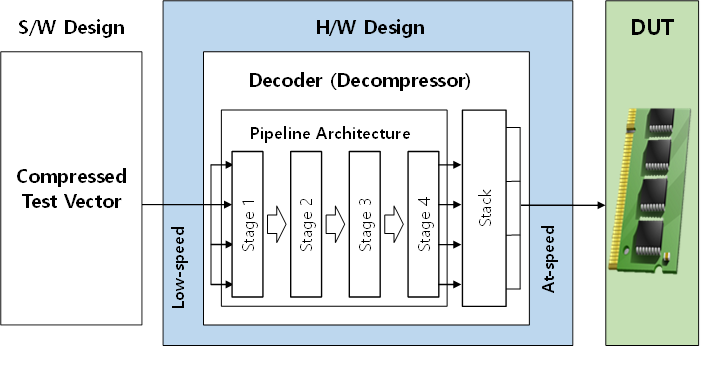

테스트 벡터 압축 및 복원 하드웨어 설계

다양한 종류의 테스트 벡터 대상으로 효율적인 압축 알고리즘의 적용 및 고속 복원 디코더 회로 설계

그림 1. 테스트 벡터 압축 H/W S/W Co-Design

- 소프트웨어 기반 테스트 벡터 압축 알고리즘 기법 구현

- 랜덤성 유무에 따른 다양한 샘플 테스트 벡터의 특성 분석 및 효율적인 압축 알고리즘 적용

- 다수의 압축된 테스트 벡터를 동시에 로드 후 병렬적으로 디코딩하여 device-under-test (DUT) 로

전송될 테스트 벡터로 복원할 수 있는 고속 디코더 회로 설계

- 파이프라이닝 기법 등을 통한 디코딩 시 추가되는 테스트 타임 오버헤드의 최소화

* 관심 있는 학생들은 강성호 교수님께 연락하여 면담 일정을 조율 및 예약하시기 바랍니다.

* 강성호 교수님 E-Mail : shkang@yonsei.ac.kr

* 면담 일정 : 2024. 12. 3 ~ 2024. 12. 5 / 2024. 12. 16 ~ 12. 18

* 종합 설계 시작일 : 2025. 1. 14 예정

* (12월 2일 추가 공지) 현재 면담이 예약된 인원을 제외하고 신청이 마감되었으니 참고 바랍니다.

2025년도 1학기 진행될 종합설계 연구테마 관련하여 안내 드립니다.

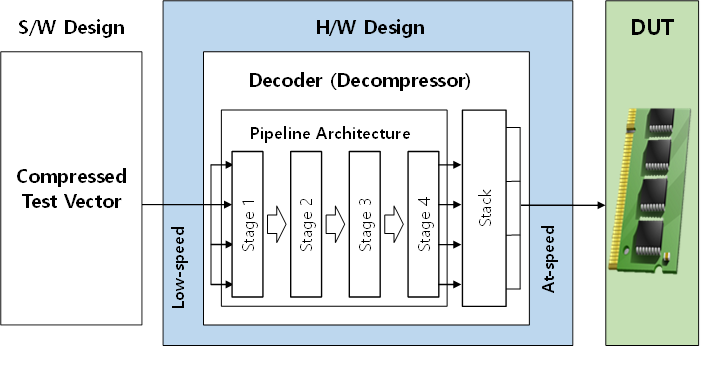

테스트 벡터 압축 및 복원 하드웨어 설계

다양한 종류의 테스트 벡터 대상으로 효율적인 압축 알고리즘의 적용 및 고속 복원 디코더 회로 설계

그림 1. 테스트 벡터 압축 H/W S/W Co-Design

- 소프트웨어 기반 테스트 벡터 압축 알고리즘 기법 구현

- 랜덤성 유무에 따른 다양한 샘플 테스트 벡터의 특성 분석 및 효율적인 압축 알고리즘 적용

- 다수의 압축된 테스트 벡터를 동시에 로드 후 병렬적으로 디코딩하여 device-under-test (DUT) 로

전송될 테스트 벡터로 복원할 수 있는 고속 디코더 회로 설계

- 파이프라이닝 기법 등을 통한 디코딩 시 추가되는 테스트 타임 오버헤드의 최소화

* 관심 있는 학생들은 강성호 교수님께 연락하여 면담 일정을 조율 및 예약하시기 바랍니다.

* 강성호 교수님 E-Mail : shkang@yonsei.ac.kr

* 면담 일정 : 2024. 12. 3 ~ 2024. 12. 5 / 2024. 12. 16 ~ 12. 18

* 종합 설계 시작일 : 2025. 1. 14 예정

* (12월 2일 추가 공지) 현재 면담이 예약된 인원을 제외하고 신청이 마감되었으니 참고 바랍니다.