2024년 2학기 전기전자 종합설계 주제 안내

Author

comsys

Date

2024-06-05 16:41

Views

791

컴퓨터 시스템 및 고신뢰성 SOC 연구실에서

2024년도 2학기 진행될 종합 설계 연구 테마 관련하여 안내 드립니다.

하드웨어 기반의 디코더 회로 설계

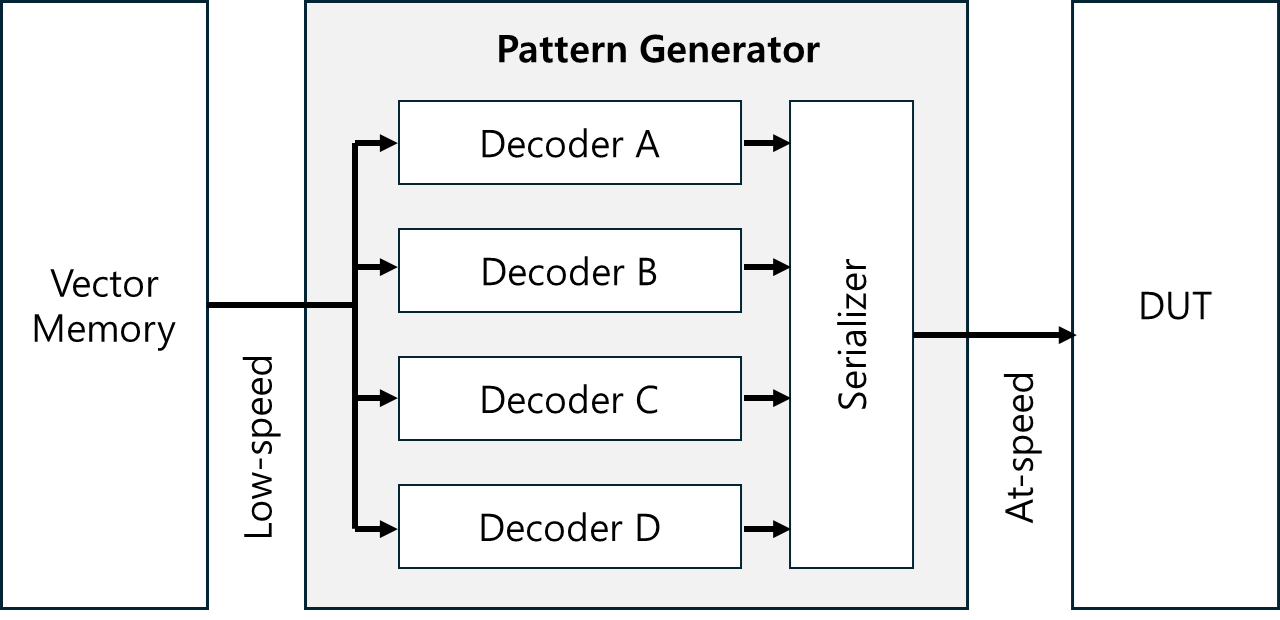

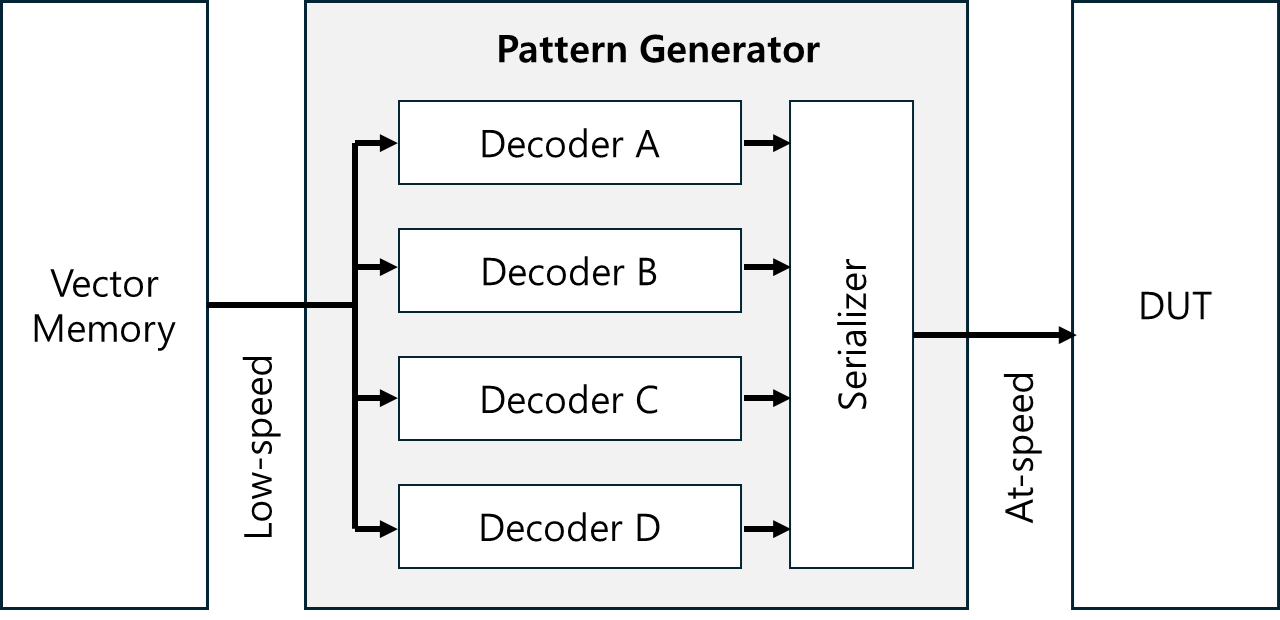

그림 A. DUT 인가 패턴 생성을 위한 병렬처리 하드웨어

- 알고리즘 기반으로 압축된 테스트 패턴의 고속 복원 디코더 회로 설계

- 복수 개의 패턴을 동시에 로드한 뒤 한번에 디코딩하는 방식으로 동작 속도를 증폭시키는 것이 설계 목표

- 파이프라이닝 기법 등을 활용하여, 압축된 패턴을 하나씩 로드하여 복원했을 때 보다 복원에 소요되는 클락 사이클 수가 감소함을 시뮬레이션을 통해 검증

- 압축 알고리즘의 경우 가변 길이 압축 방식(run-length encoding 등)방식과 고정 길이 압축 방식 구현

2024년도 2학기 진행될 종합 설계 연구 테마 관련하여 안내 드립니다.

하드웨어 기반의 디코더 회로 설계

그림 A. DUT 인가 패턴 생성을 위한 병렬처리 하드웨어

- 알고리즘 기반으로 압축된 테스트 패턴의 고속 복원 디코더 회로 설계

- 복수 개의 패턴을 동시에 로드한 뒤 한번에 디코딩하는 방식으로 동작 속도를 증폭시키는 것이 설계 목표

- 파이프라이닝 기법 등을 활용하여, 압축된 패턴을 하나씩 로드하여 복원했을 때 보다 복원에 소요되는 클락 사이클 수가 감소함을 시뮬레이션을 통해 검증

- 압축 알고리즘의 경우 가변 길이 압축 방식(run-length encoding 등)방식과 고정 길이 압축 방식 구현