# **Chapter # 4: Programmable and Steering Logic**

#### **Chapter Overview**

- PALs and PLAs

- Non-Gate Logic

Switch Logic

Multiplexers/Selecters and Decoders

Tri-State Gates/Open Collector Gates

ROM

- Combinational Logic Design Problems Seven Segment Display Decoder Process Line Controller Logical Function Unit Barrel Shifter

### **PALs and PLAs**

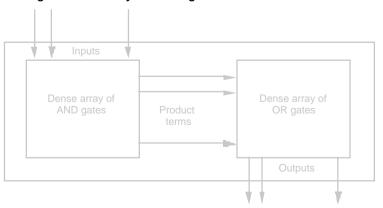

Pre-fabricated building block of many AND/OR gates (or NOR, NAND) "Personalized" by making or breaking connections among the gates

#### Programmable Array Block Diagram for Sum of Products Form

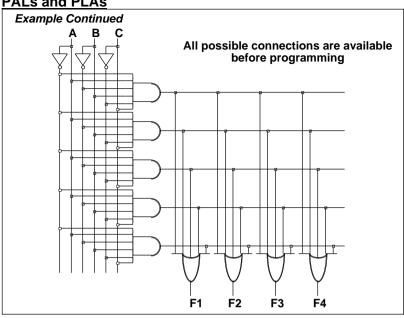

#### **PALs and PLAs**

Key to Success: Shared Product Terms

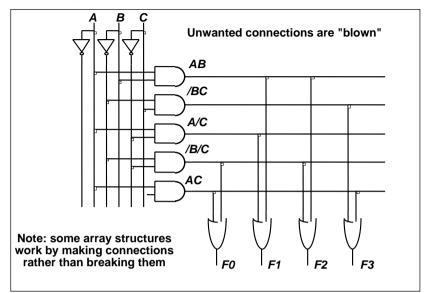

#### **Equations**

F0 = A + B'C'

Example: F1 = A C' + A BF2 = B' C' + A B

F3 = B'C + AB

#### Input Side:

1 = asserted in term

0 = negated in term

- = does not participate

#### Output Side:

1 = term connected to output

0 = no connection to output

# Personality Matrix

| Product         | Inputs |   |   | 0     | utpu  | ıts   |       |       |

|-----------------|--------|---|---|-------|-------|-------|-------|-------|

| term            | Α      | В | С | $F_0$ | $F_1$ | $F_2$ | $F_3$ |       |

| ΑВ              | 1      | 1 | - | 0     | (1)   | (     | 0     |       |

| BC              | -      | 0 | 1 | 0     | 0     | 0     | 1     | Reuse |

| $A\overline{C}$ | 1      | _ | 0 | 0     | 1     | 0     | 0     | of    |

| ВС              | -      | 0 | 0 | (1)   | 0     | (1)   | 0/    | terms |

| Α               | 1      | - | - |       | 0     | 0     |       |       |

4-1

#### **PALs and PLAs**

#### **PALs and PLAs**

Example Continued

4-5

4-6

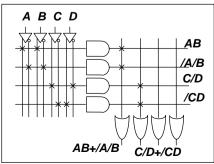

# **PALs and PLAs**

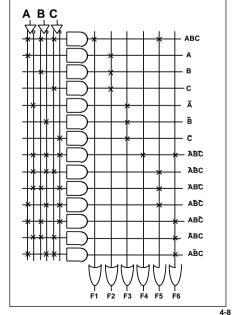

Alternative representation for high fan-in structures

**Short-hand notation** so we don't have to draw all the wires!

Notation for implementing F0 = A B + A' B' F1 = C D' + C' D

#### **PALs and PLAs**

Design Example

Multiple functions of A, B, C

F1 = A B C

F2 = A + B + C

F3 = A B C

F4 = A + B + C

F5 = A xor B xor C

F6 = A xor B xor C

#### **PALs and PLAs**

What is difference between Programmable Array Logic (PAL) and Programmable Logic Array (PLA)?

PAL concept: implemented by Monolithic Memories

(substrate is active materialsuch as semiconductor silicon)

programmable AND array but constrained topology of the OR Array

connections between product terms are hardwired

the higher the OR gate fanins, the fewer the functional outputs from

PAL

A given column of the OR array has access to only a subset of the possible product terms

PLA concept : generalized topologies in AND and OR planes take advantage of shared product terms slower

#### **PALs and PLAs**

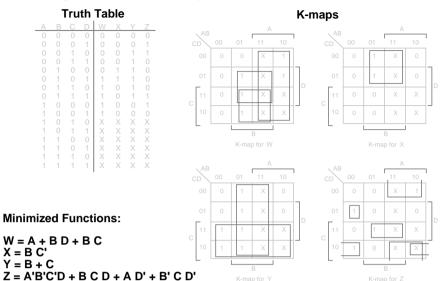

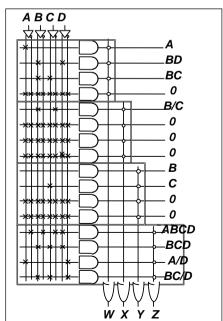

Design Example: BCD to Gray Code Converter

### **PALs and PLAs**

Programmed PAL:

**PALs and PLAs**

Code Converter Discrete Gate Implementation

4 SSI Packages vs. 1 PLA/PAL Package!

4 product terms per each OR gate

4-11

4-9

#### **PALs and PLAs**

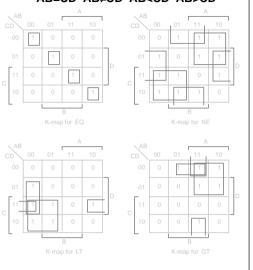

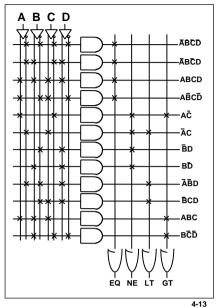

Another Example: Magnitude Comparator

#### AB=CD AB≠CD AB<CD AB>CD

#### **Non-Gate Logic**

Introduction

AND-OR-Invert PAL/PLA

Generalized Building Blocks Beyond Simple Gates

#### Kinds of "Non-gate logic":

- switching circuits built from CMOS transmission gates

- multiplexer/selecter functions

- decoders

- tri-state and open collector gates

- read-only memories

4-14

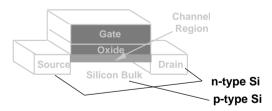

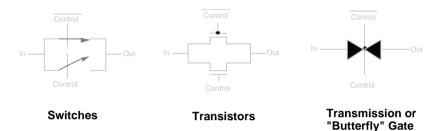

# **Steering Logic: Switches**

Voltage Controlled Switches

"n-Channel MOS"

Metal Gate, Oxide, Silicon Sandwich

Diffusion regions: negatively charged ions driven into Si surface

Si Bulk: positively charged ions

By "pulling" electrons to the surface, a conducting channel is formed

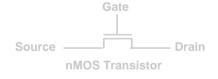

### **Steering Logic**

**Voltage Controlled Switches**

Logic 1 on gate, Source and Drain connected

Logic 0 on gate, Source and Drain connected

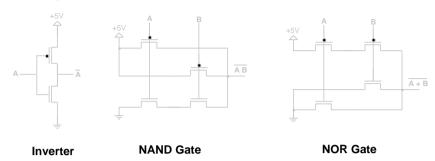

#### Logic Gates from Switches

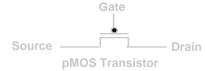

Pull-up network constructed from pMOS transistors

Pull-down network constructed from nMOS transistors

#### **Steering Logic**

#### Inverter Operation

Input is 1 Pull-up does not conduct Pull-down conducts Output connected to GND

Input is 0

Pull-up conducts

Pull-down does not conduct

Output connected to VDD

4-17

### **Steering Logic**

#### NAND Gate Operation

A = 1, B = 1

Pull-up network does not conduct

Pull-down network conducts

Output node connected to GND

A = 0, B = 1

Pull-up network has path to VDD

Pull-down network path broken

Output node connected to VDD

# Steering Logic

#### **NOR Gate Operation**

A = 0, B = 0 Pull-up network conducts Pull-down network broken Output node at VDD

A = 1, B = 0 Pull-up network broken Pull-down network conducts Output node at GND

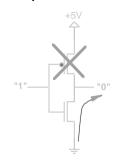

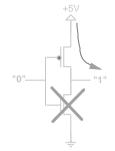

**CMOS Transmission Gate**

nMOS transistors good at passing 0's but bad at passing 1's produce weak 1

pMOS transistors good at passing 1's but bad at passing 0's produce weak 0

perfect "transmission" gate places these in parallel:

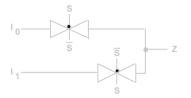

#### **Steering Logic**

Selection Function/Demultiplexer Function with Transmission Gates

Selector:

Choose I0 if S = 0

Choose I1 if S = 1

Demultiplexer: I to Z0 if S = 0 I to Z1 if S = 1

4-21

4-22

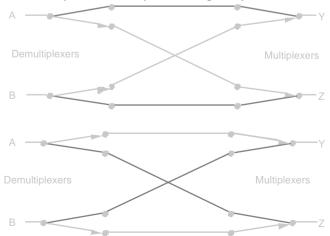

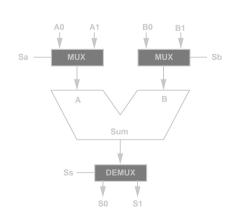

# **Steering Logic**

Use of Multiplexer/Demultiplexer in Digital Systems

So far, we've only seen point-to-point connections among gates

Mux/Demux used to implement multiple source/multiple destination interconnect

# **Steering Logic**

Well-formed Switching Networks

Problem with the Demux implementation: multiple outputs, but only one connected to the input!

The fix: additional logic to drive every output to a known value

Never allow outputs to "float"

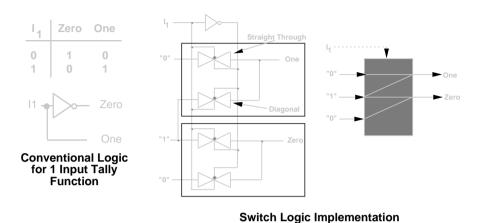

#### Complex Steering Logic Example

#### N Input Tally Circuit: count # of 1's in the inputs

of Tally Function

4-25

#### **Steering Logic**

#### Complex Steering Logic Example

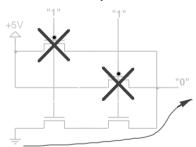

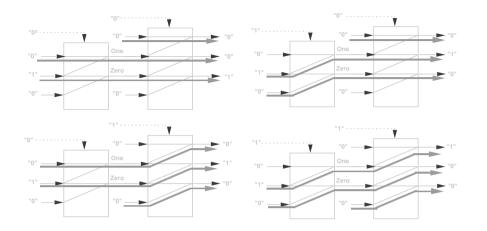

#### **Operation of the 1 Input Tally Circuit**

Input is 0, straight through switches enabled

4-26

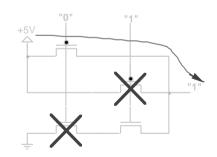

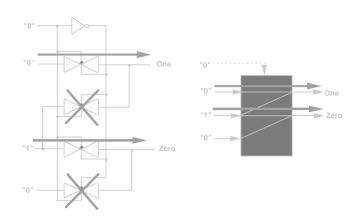

# **Steering Logic**

# Complex Steering Logic Example Operation of 1 input Tally Circuit

Input = 1, diagonal switches enabled

### **Steering Logic**

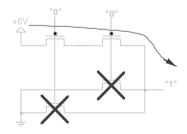

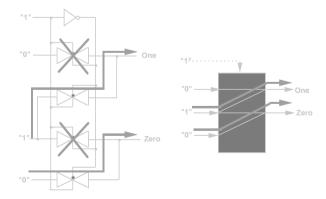

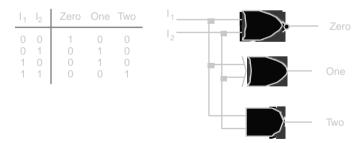

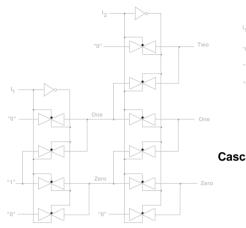

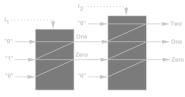

# Complex Steering Logic Example Extension to the 2-input case

Conventional logic implementation

Complex Steering Logic Example

Switch Logic Implementation: 2-input Tally Circuit

Cascade the 1-input implementation!

#### **Steering Logic**

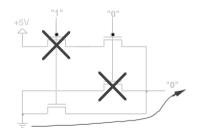

Complex Steering Logic Example **Operation of 2-input implementation**

4-29

# **Multiplexers/Selectors**

Use of Multiplexers/Selectors

**Multi-point connections**

**Multiple input sources**

**Multiple output destinations**

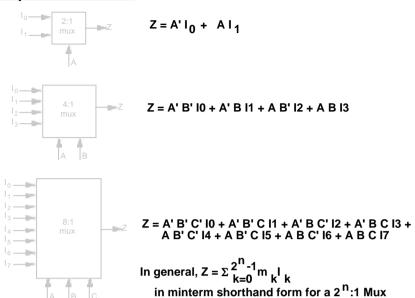

# Multiplexers/Selectors General Concept

2<sup>n</sup> data inputs, n control inputs, 1 output used to connect 2<sup>n</sup> points to a single point control signal pattern form binary index of input connected to output

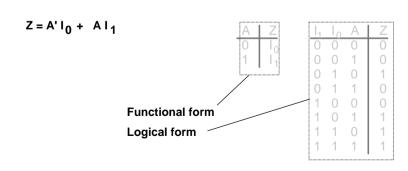

Two alternative forms for a 2:1 Mux Truth Table

#### **Multiplexers/Selectors**

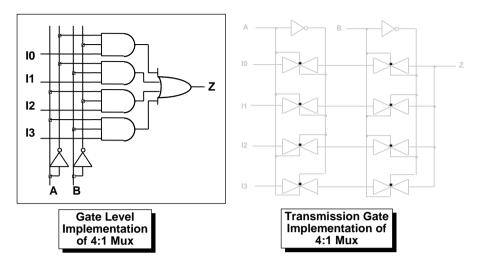

#### **Multiplexers/Selectors**

Alternative Implementations

thirty six transistors

twenty transistors

4-33

4-34

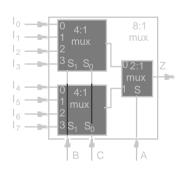

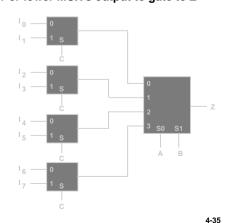

# Multiplexer/Selector

Large multiplexers can be implemented by cascaded smaller ones

Alternative 8:1 Mux Implementation

Control signals B and C simultaneously choose one of I0-I3 and I4-I7

Control signal A chooses which of the upper or lower MUX's output to gate to Z

### **Multiplexer/Selector**

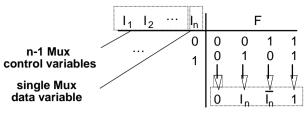

Multiplexers/selectors as a general purpose logic block

2 <sup>n-1</sup>:1 multiplexer can implement any function of n variables

n-1 control variables; remaining variable is a data input to the mux

Example:

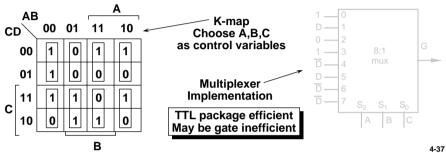

# Multiplexer/Selector

Generalization

Four possible configurations of the truth table rows

Can be expressed as a function of In, 0, 1

#### Example:

G(A,B,C,D) can be implemented by an 8:1 MUX:

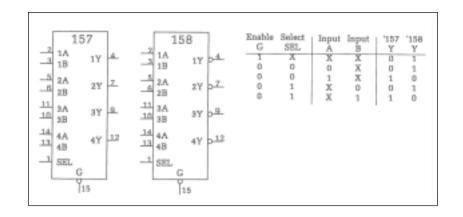

#### Multiplexer/Selector

• TTL quad 2:1 multiplexers with enable

4-38

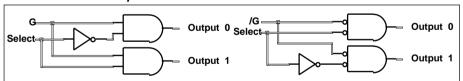

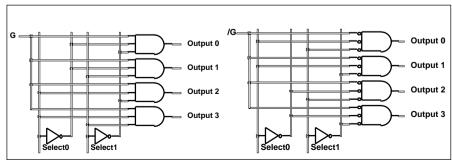

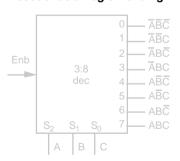

# **Decoders/Demultiplexers**

Decoder: single data input, n control inputs, 2<sup>n</sup> outputs

control inputs (called select S) represent Binary index of output to which the input is connected

data input usually called "enable" (G)

| 1:2 Decoder:                                     | 3:8 Decoder:                                                         |

|--------------------------------------------------|----------------------------------------------------------------------|

| $O0 = G \cdot \overline{S}; O1 = G \cdot S$      | $O0 = G \cdot \overline{S0} \cdot \overline{S1} \cdot \overline{S2}$ |

| 2:4 Decoder:                                     | $O1 = G \cdot \overline{S0} \cdot \overline{S1} \cdot S2$            |

| $O0 = G \cdot \overline{S0} \cdot \overline{S1}$ | $O2 = G \cdot \overline{S0} \cdot S1 \cdot \overline{S2}$            |

| 01 = G • <del>S0</del> • S1                      | O3 = G • S0 • S1 • S2                                                |

| O2 = G • S0 • S1                                 | O4 = G • S0 • S1 • S2                                                |

| O3 = G • S0 • S1                                 | O5 = G • S0 • S1 • S2                                                |

|                                                  | O6 = G • S0 • S1 • S2                                                |

|                                                  | 07 = G • S0 • S1 • S2                                                |

#### **Decoders/Demultiplexers**

Alternative Implementations

1:2 Decoder, Active High Enable

1:2 Decoder, Active Low Enable

2:4 Decoder, Active High Enable

2:4 Decoder, Active Low Enable

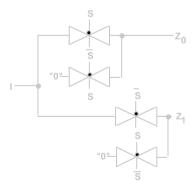

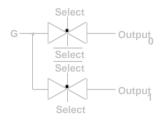

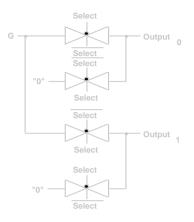

#### **Decoders/Demultiplexers** Switch Logic Implementations

Naive, Incorrect Implementation

All outputs not driven at all times

**Correct 1:2 Decoder Implementation**

#### **Decoders/Demultiplexers**

Switch Implementation of 2:4 Decoder

Operation of 2:4 Decoder S0 = 0, S1 = 0one straight thru path three diagonal paths

4-42

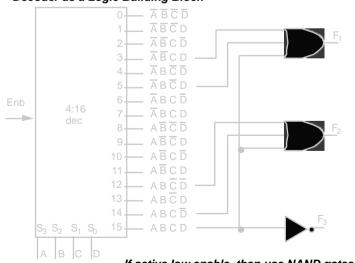

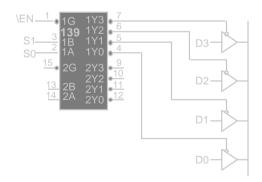

#### Decoder/Demultiplexer

Decoder as a Logic Building Block

Decoder Generates Appropriate Minterm based on Control Signals

#### **Example Function:**

F1 = A' B C' D + A' B' C D + A B C D

F2 = A B C' D' + A B C

F3 = (A' + B' + C' + D')

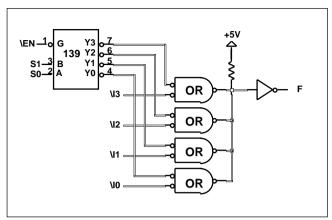

# **Decoder/Demultiplexer**

Decoder as a Logic Building Block

If active low enable, then use NAND gates!

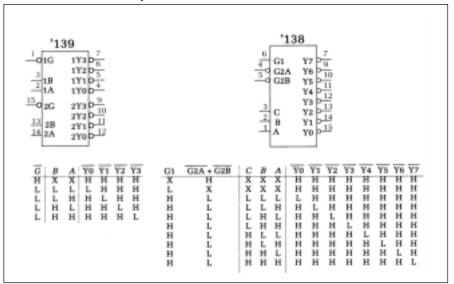

#### Decoder/Demultiplexer

• TTL decoder components

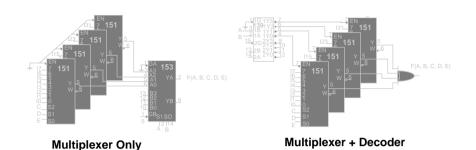

#### Multiplexers/Decoders

Alternative Implementations of 32:1 Mux

4-45

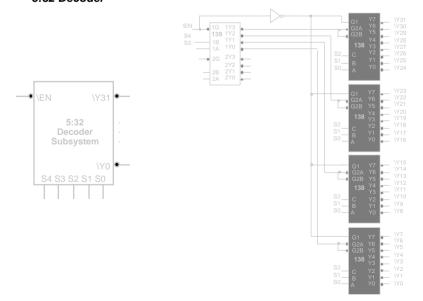

#### Multiplexers/Decoders

5:32 Decoder

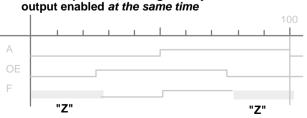

# **Tri-State and Open-Collector**

The Third State

Logic States: "0", "1"

Don't Care/Don't Know State: "X" (must be some value in real circuit!)

Third State: "Z" — high impedance — infinite resistance, no connection

Tri-state gates: output values are "0", "1", and "Z" additional input: output enable (OE)

When OE is high, this gate is a non-inverting "buffer"

When OE is low, it is as though the gate was disconnected from the output!

This allows more than one gate to be connected to the same output wire, as long as only one has its output enabled at the same time

Non-inverting buffer's timing waveform

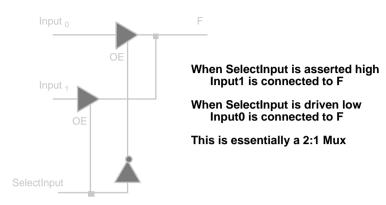

#### **Tri-state and Open Collector**

Using tri-state gates to implement an economical multiplexer:

**Switch Level Implementation** of tri-state gate

Active low tri-state enables plus inverting tri-state buffers

4-50

# **Tri-State and Open Collector**

4:1 Multiplexer, Revisited

Decoder + 4 tri-state Gates

# **Tri-State and Open Collector**

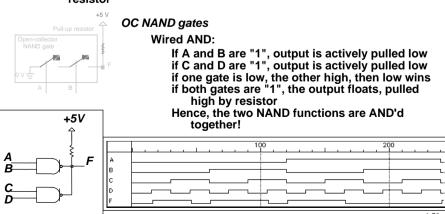

**Tri-state and Open Collector** Alternative Tri-state Fragment

**Open Collector**

another way to connect multiple gates to the same output wire

gate only has the ability to pull its output low; it cannot actively drive the wire high

this is done by pulling the wire up to a logic 1 voltage through a resistor

#### **Tri-State and Open Collector**

#### 4:1 Multiplexer

**Decoder + 4 Open Collector Gates**

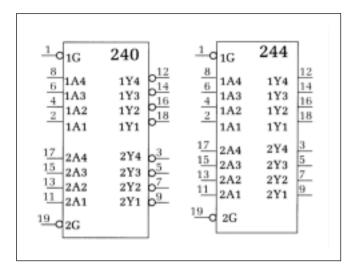

#### **Tri-State and Open Collector**

#### • TTL tri-state buffers

4-53

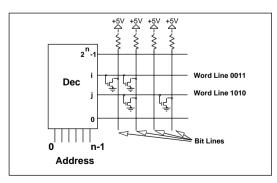

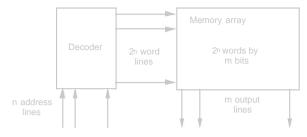

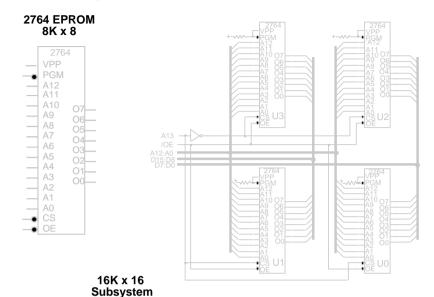

#### **Read-Only Memories**

ROM: Two dimensional array of 1's and 0's

Row is called a "word"; index is called an "address"

Width of row is called bit-width or wordsize

Address is input, selected word is output

**Internal Organization**

#### **Read-Only Memories**

Example: Combination Logic Implementation

F0 = A' B' C + A B' C' + A B' C

F1 = A' B' C + A' B C' + A B C

F2 = A' B' C' + A' B' C + A B' C'

F3 = A' B C + A B' C' + A B C'

#### **Read-Only Memories**

Not unlike a PLA structure with a fully decoded AND array!

#### ROM vs. PLA:

**ROM** approach advantageous when

- (1) design time is short (no need to minimize output functions)

- (2) most input combinations are needed (e.g., code converters)

- (3) little sharing of product terms among output functions

ROM problem: size doubles for each additional input, can't use don't cares

PLA approach advantangeous when

- (1) design tool like espresso is available

- (2) there are relatively few unique minterm combinations

- (3) many minterms are shared among the output functions

PAL problem: constrained fan-ins on OR planes

4-57

#### **Read-Only Memories**

4-58

# **Combinational Logic Word Problems**

General Design Procedure

- Understand the Problem

what is the circuit supposed to do?

write down inputs (data, control) and outputs

draw block diagram or other picture

- 2. Formulate the Problem in terms of a truth table or other suitable design representation truth table or waveform diagram

- 3. Choose Implementation Target ROM, PAL, PLA, Mux, Decoder + OR, Discrete Gates

- 4. Follow Implementation Procedure K-maps, espresso, misll

# **Combinational Logic Word Problems**

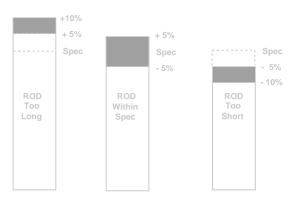

**Process Line Control Problem**

Statement of the Problem

Rods of varying length (+/-10%) travel on conveyor belt Mechanical arm pushes rods within spec (+/-5%) to one side Second arm pushes rods too long to other side Rods too short stay on belt

3 light barriers (light source + photocell) as sensors

Design combinational logic to activate the arms

Understanding the Problem

Inputs are three sensors, outputs are two arm control signals

Assume sensor reads "1" when tripped, "0" otherwise

Call sensors A, B, C

Draw a picture!

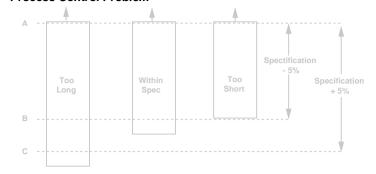

Process Control Problem

Where to place the light sensors A, B, and C to distinguish among the three cases?

Assume that A detects the leading edge of the rod on the conveyor

Combinational Logic Word Problems

Process Control Problem

A to B distance place apart at specification - 5%

A to C distance placed apart at specification +5%

#### **Combinational Logic Word Problems**

**Process Control Problem**

| Α | В | C | Function  |

|---|---|---|-----------|

| 0 | 0 | 0 | X         |

| 0 | 0 | 1 | X         |

| 0 | 1 | 0 | X         |

| 0 | 1 | 1 | X         |

| 1 | 0 | 0 | too short |

| 1 | 0 | 1 | X         |

| 1 | 1 | 0 | in spec   |

| 1 | 1 | 1 | too long  |

Truth table and logic implementation now straightforward

"too long" = A B C

(all three sensors tripped)

"in spec" = A B C'

(first two sensors tripped)

# **Combinational Logic Word Problems**

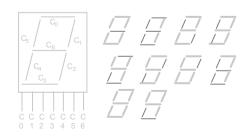

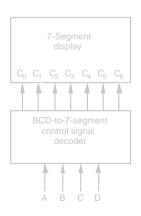

BCD to 7 Segment Display Controller

Understanding the problem:

input is a 4 bit bcd digit

output is the control signals for the display

4 inputs A, B, C, D

7 outputs C0 ~ C6

**Block Diagram**

4-61

BCD to 7 Segment Display Controller

| A | В | IC | D | l CO | C1 | C2 | C3 | C4 | C5 | C6 |

|---|---|----|---|------|----|----|----|----|----|----|

| 1 | 0 | Ö  | ň | 4    | 4  | 1  | 4  | 4  | 4  | n  |

|   | - | 0  | 4 |      | ,  | 4  |    |    |    | •  |

| 0 | 0 | U  | 1 | 0    | 1  | 1  | 0  | 0  | 0  | 0  |

| 0 | 0 | 1  | 0 | 1    | 1  | 0  | 1  | 1  | 0  | 1  |

| 0 | 0 | 1  | 1 | 1    | 1  | 1  | 1  | 0  | 0  | 1  |

| 0 | 1 | 0  | 0 | 0    | 1  | 1  | 0  | 0  | 1  | 1  |

| 0 | 1 | 0  | 1 | 1    | 0  | 1  | 1  | 0  | 1  | 1  |

| 0 | 1 | 1  | 0 | 1    | 0  | 1  | 1  | 1  | 1  | 1  |

| 0 | 1 | 1  | 1 | 1    | 1  | 1  | 0  | 0  | 0  | 0  |

| 1 | 0 | 0  | 0 | 1    | 1  | 1  | 1  | 1  | 1  | 1  |

| 1 | 0 | 0  | 1 | 1    | 1  | 1  | 0  | 0  | 1  | 1  |

| 1 | 0 | 1  | 0 | X    | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  |

| 1 | 0 | 1  | 1 | X    | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  |

| 1 | 1 | 0  | 0 | X    | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  |

| 1 | 1 | 0  | 1 | Χ    | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  |

| 1 | 1 | 1  | 0 | Χ    | Χ  | Χ  | Χ  | Χ  | Χ  | Χ  |

| 1 | 1 | 1  | 1 | Х    | Χ  | Χ  | Χ  | χ  | Χ  | Χ  |

|   |   |    |   |      |    |    |    |    |    |    |

Formulate the problem in terms of a truth table

**Choose implementation** target:

if ROM, we are done

don't cares imply PAL/PLA may be attractive

Follow implementation procedure:

hand reduced K-maps

vs.

espresso

4-65

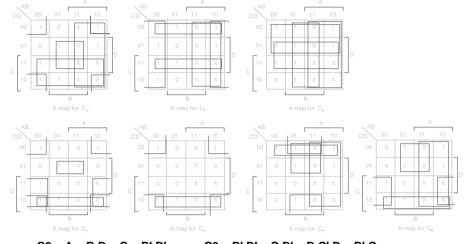

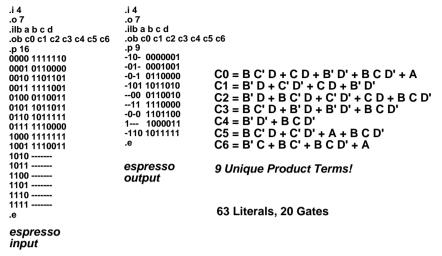

#### **Combinational Logic Word Problems** BCD to 7 Segment Display Controller

C0 = A + BD + C + B'D'C1 = A + C' D' + C D + B'

C2 = A + B + C' + D

14 Unique Product Terms

C3 = B' D' + C D' + B C' D + B' C C4 = B' D' + C D

C5 = A + C' D' + B D' + B C'

C6 = A + C D' + B C' + B' C

4-66

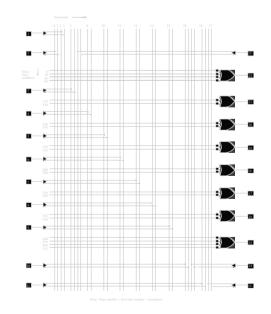

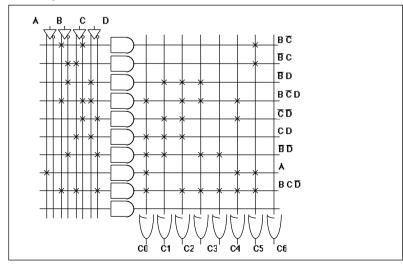

# **Combinational Logic Word Problems**

BCD to 7 Segment Display Controller

16H8PAL Can Implement the function

# **Combinational Logic Word Problems**

BCD to 7 Segment Display Controller

14H8PAL **Cannot Implement** the function

BCD to 7 Segment Display Controller

F100 PAL programming map

# **Combinational Logic Word Problems**

BCD to 7 Segment Display Controller

4-70

#### **Combinational Logic Word Problems**

BCD to 7 Segment Display Controller

#### **PLA Implementation**

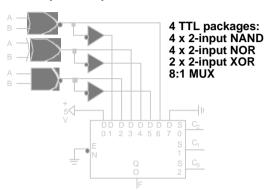

# Combinational Logic Word Problems

BCD to 7 Segment Display Controller

**Multilevel Implementation**

**Logical Function Unit**

Statement of the Problem:

3 control inputs: C0, C1, C2 2 data inputs: A, B

1 output: F

| CO | C1 | C2 | F       | Comments     |

|----|----|----|---------|--------------|

| 0  | 0  | 0  | 1       | always 1     |

| 0  | 0  | 1  | A + B   | logical or   |

| 0  | 1  | 0  | A-B     | logical nand |

| 0  | 1  | 1  | A xor B | logical xor  |

| 1  | 0  | 0  | A xnorB | logical xnor |

| 1  | 0  | 1  | A-B     | logical and  |

| 1  | 1  | 0  | A+B     | logical nor  |

| 1  | 1  | 1  | 0       | always 0     |

|    |    |    |         | -            |

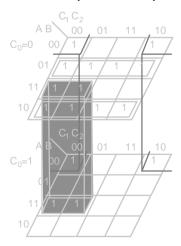

#### **Combinational Logic Word Problems**

Logical Function Unit

Formulate as a truth table

Choose implementation technology 5-variable K-map espresso multiplexor implementation

4-73

#### **Combinational Logic Word Problems**

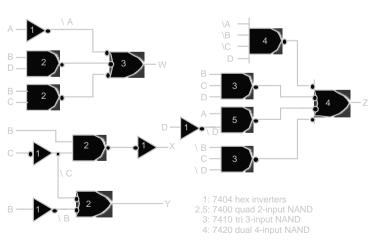

**Logical Function Unit**

#### Follow implementation procedure

F = C2' A' B' + C0' A B' + C0' A' B + C1' A B

5 gates, 5 inverters

Also four packages: 4 x 3-input NAND 1 x 4-input NAND

Alternative: 32 x 1-bit ROM

single package

# **Combinational Logic Word Problems**

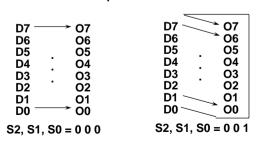

8-Input Barrel Shifter

#### Specification:

Inputs: D7, D6, ~ D0 Outputs: O7, O6, ~ O0 Control: S2, S1, S0

shift input the specified number of positions to the right

#### Understand the problem:

S2, S1, S0 = 0.10

8-Input Barrel Shifter

| Function Table | S2 | S1 | SO | 07 | 06 | 05 | 04 | 03 | 02 | 01 | 00 |

|----------------|----|----|----|----|----|----|----|----|----|----|----|

| runction rable | 0  | 0  | 0  | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|                | 0  | 0  | 1  | D6 | D5 | D4 | D3 | D2 | D1 | D0 | D7 |

|                | 0  | -1 | 0  | D5 | D4 | D3 | D2 | D1 | D0 | D7 | D6 |

|                | 0  | 1  | 1  | D4 | D3 | D2 | D1 | D0 | D7 | D6 | D5 |

|                | 1  | 0  | 0  | D3 | D2 | D1 | D0 | D7 | D6 | D5 | D4 |

|                | 1  | 0  | 1  | D2 | D1 | D0 | D7 | D6 | D5 | D4 | D3 |

|                | 1  | 1  | 0  | D1 | D0 | D7 | D6 | D5 | D4 | D3 | D2 |

|                | 1  | 1  | 1  | D0 | D7 | D6 | D5 | D4 | D3 | D2 | D1 |

|                |    |    |    |    |    |    |    |    |    |    |    |

# Boolean equations

#### **Combinational Logic Word Problems**

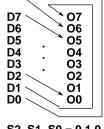

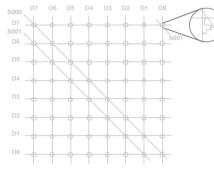

8-Input Barrel Shifter

Straightforward gate logic implementation OR

8 by 8:1 multiplexer (wiring mess!) OR

Switch logic

D6 S010 D5 S011 D4 S100 D3 S100 D2 S110 D1 S111 D1 S111 D1 S111 D1 S111

**Crosspoint switches**

**Fully Wired crosspoint switch**

4-77

# **Chapter Review**

• Non-Simple Gate Logic Building Blocks:

PALs/PLAs

Multiplexers/Selecters

**Decoders**

**ROMs**

Tri-state, Open Collector

• Combinational Word Problems:

**Understand the Problem**

Formulate in terms of a Truth Table

Choose implementation technology

Implement by following the design procedure